It has been a long time coming, and it might have been better if this had been done a decade ago. But with a big injection of open source spirit from its acquisition of Red Hat, IBM is finally taking the next step and open sourcing the instruction set architecture of its Power family of processors.

Big Blue is also moving the OpenPower Foundation, which it formed with Google, Mellanox Technologies, Nvidia, and Tyan to help create an ecosystem around the Power architecture six years ago this month, under the administrative control of the Linux Foundation. (Considering how many open source projects are under the control of the Linux Foundation, perhaps it is time for that organization to consider a name change. The Open Foundation is probably appropriate, and probably already owned by someone else.)

In any event, if you have ever wanted to create your own Power processor and was lamenting how expensive it might be to license the technology from IBM, now is your chance.

IBM’s long journey to opening up the Power architecture began a long time ago, starting with the creation of the PowerPC Alliance between Apple, IBM, and Motorola back in 1991, just as Big Blue was starting to get serious about the Power architecture for RS/6000 Unix systems – Unix was all the rage then, and Sun Microsystems and Hewlett Packard were circling IBM’s proprietary mainframes and minicomputers like starving wolves, with a very lean and hungry Oracle snarling nearby. Behind the scenes, IBM was preparing to move its proprietary AS/400 enterprise systems to a common hardware platform with the RS/6000, a credible Windows Servers was years away (and would very briefly run on Power iron), and a young Linus Torvalds had just created the first Linux kernel (which would eventually be the key to keeping Power iron alive in HPC centers in particular and in some enterprise datacenters).

The history is long and complex, but suffice it to say that Motorola and IBM both had their challenges bringing server-class processors to market and the move to 64-bits was particularly difficult. Interestingly, it was IBM’s AS/400 processor team in Rochester, Minnesota which saved the day by creating a very good 64-bit PowerPC chip that also had a double-pumped vector processor embedded in it, and it is this processor, not the ones designed by the AIX people down in Austin, that is the very kernel of all Power chips and systems that have followed since. Eventually Sun Microsystems went up on the rocks with its UltraSparc-III systems, and Hewlett Packard and Intel created Itanium, which had its own litany of woes, and this left the door wide open for IBM to be a spoiler in the early 2000s. And it was just then, back in 2001, when IBM got its first dual-core chip and its first processor to clock above 1 GHz out the door – that would be the Power4 “GigaProcessor” – and IBM brought the hammer down in Unix, delivering twice the bang for the buck as Sun and HP did in Unix, eating market share like crazy.

At the same time all of this was going on, the Motorola 68000 series of chips, which were at the heart of Apple PCs as well as myriad kinds and untold millions of embedded controllers. Arm may rule in controllers today, but back then its was Motorola 68Ks, and the kind of unified processor architecture spanning from embedded devices to datacenter gear was first done – and actually realized – with the PowerPC architecture.

Of course, since then, the Unix market has been largely replaced by X86 systems running Linux and Windows Server, and Sparc from Sun and PA-RISC from HP, and Itanium from Intel are all dead. Motorola has ceded the embedded controller market to Arm, and IBM has been trying to breathe some life into Power, first through the Power.org in 2004 and the OpenPower Foundation in 2013. With each move, IBM has opened up its technology a little more and broadened its appeal. It is a question as to whether this will be enough, with an ascending AMD providing an alternative to Intel processors and the Arm collective fielding many good processors, all using Arm licenses and many adding their own special tweaks to the Arm designs while not violating the Arm architecture.

No one is saying that the OpenPower Foundation will have an easy time growing its ecosystem, despite the many architectural advantages that Power holds over other ISAs, but it now has an easier time than a more closed architecture has. It doesn’t hurt that the Power ISA is being given away royalty free, either.

“We started OpenPower six years ago because the industry was seeing the decline of Moore’s Law, and we were seeing the need for more powerful systems to support HPC, artificial intelligence, and data analytics,” Ken King, general manager of OpenPower at IBM, tells The Next Platform. “We needed to find other ways to drive system performance, and with limitations on the processor, the ability to integrate and innovate up and down the stack was becoming more critical. This led to things like NVLink with Nvidia, a close relationship with Mellanox on interconnects, and OpenCAPI for other devices, and we have seen some progress here. But we are also seeing a shift in the industry, with companies moving to more open hardware. IBM opening up Power to the point where we would license the CPU RTL to others so they could design their own processors was limited in its effect because there were not that many people who wanted to spend many hundreds of millions of dollars – not for license fees, but for full development – to create their own high-end CPU. We did make some progress in opening up our reference designs, and there are over 20 vendors who are now making Power-based systems. We are seeing interesting developments with the nascent RISC-V architecture, and hyperscalers are hiring their own chip designers and building their own CPUs and interconnects. They are getting into the hardware space, even if they are not going to be hardware vendors, to drive that performance.”

In that environment, now is as good time as any to get the Power ISA opened up and see what kind of uptake it might have against RISC-V and Arm and a closed X86 architecture from AMD and Intel.

To be precise about what IBM is doing, it is opening up the Power ISA and giving it to the OpenPower Foundation royalty free with patent rights, and that means companies can implement a chip using the Power ISA without having to pay IBM or OpenPower a dime, and they have patent rights to what they develop. Companies have to maintain compatibility with the instruction set, King explains, and there are a whole set of compatibility requirements, which we presume are precisely as stringent as Arm and are needed to maintain runtime compatibility should many Power chips be developed, as IBM hopes will happen.

The OpenPower Foundation, working under the Linux Foundation umbrella, will have an open governance model, with IBM having precisely the same one vote as other OpenPower Foundation members as to what changes can be made to the Power ISA in the future. IBM will have retain the right to make whatever changes that it wants to the architecture to suit its own needs, but all other changes will require a majority vote of the members to ensure compatibility. “Everything has to stay in the compliance guidelines because we do not want a bunch of fragmentation,” says King. This presumably also applies to Big Blue. If companies want to make a non-compliant change, it takes a unanimous vote of the members to do so. For instance, this may be for some specific set of instructions for a very precise workload set. Anyone can do a custom chip, too, but they will fall out of compliance with the ecosystem.

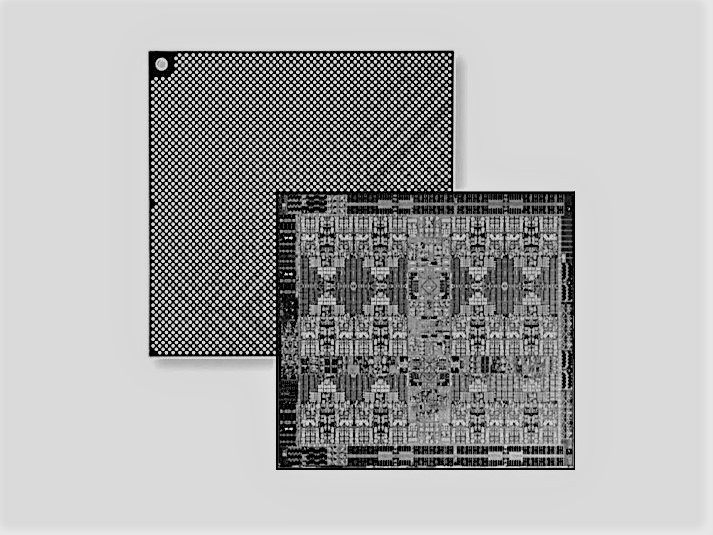

In addition to all of this, IBM is providing a softcore model of the Power ISA that has been implemented on FPGAs – presumably from Xilinx, not Intel’s Altera devices – that people can play around with.

In addition to this, IBM is also taking its OpenCAPI accelerator interface and its OpenCAPI Memory Interface variant, which is a key feature of the Power9’ (that’s a prime symbol, not a typo) processor that is coming out sometime this year, and it is actually contributing the RTL for these reference designs to the OpenCAPI Consortium, which is independent from OpenPower.

Some work needs to be done to reduce the number of communication methods and protocols that are being employed to link CPUs to each other, to accelerators, and to storage. Gen-Z, CCIX, CXL, OpenCAPI, NVLink, Infinity Fabric – the list keeps getting longer and the differences between them all are disruptive in a bad way. We need one or two standards, maybe. Perhaps this last bit is a step in getting us there. IBM just wants for companies to make OMI memory, which we have talked about before and which we will be detailing shortly based on a presentation that IBM made this week at Hot Chips. OpenCAPI memory may be the best way to get most of the bandwidth benefits of HBM memory without having to resort to stacking up and packing it up, but keeping it in DIMM form factors.

And so, right here right now, King is extending the olive branch out to Intel, much as it did back in the late 1990s when InfiniBand was created largely by Intel and IBM as a replacement for the PCI-Express bus.

“OpenCAPI and OMI are architecture agnostic, and the goal is to enable others to create their own coherent accelerator and memory interfaces in an open standards environment,” says King. “We are hoping over time – and we have been having these discussions – that with OpenCAPI we are able to work with Intel and converge OpenCAPI and CXL to converge them into one, common standard. And there is a lot of interest in that, without getting into the specifics.”

We suspect that Google, Facebook, and maybe a few others have some good ideas about how this might get done, and that this time around, they will have a big say on how these standards will converge. One thing is for sure: They won’t tolerate six standards when one or two will do.